Inductively Coupled Plasma (ICP) etching is a cornerstone technology in the fabrication of micro and nanoscale devices, particularly for silicon-based microelectronics, microelectromechanical systems (MEMS), and nanotechnology. This advanced plasma etching technique leverages high-density plasma to achieve precise material removal with high anisotropy, enabling the creation of intricate structures critical for modern semiconductor devices. Silicon, as the dominant material in microelectronics, benefits from ICP etching due to its ability to produce high-aspect-ratio features, smooth sidewalls, and excellent selectivity. This article explores the principles, mechanisms, process parameters, applications, and advancements in ICP etching of silicon, emphasizing its role in micro and nanoscale device fabrication.

Principles of ICP Etching

ICP etching is a dry etching technique that utilizes a plasma generated by an inductively coupled radiofrequency (RF) source. Unlike traditional reactive ion etching (RIE), which relies on capacitive coupling, ICP etching employs an inductive coil to transfer energy to the plasma, resulting in higher plasma densities (10^11–10^12 ions/cm³) and lower ion energies. This decoupling of plasma generation and ion energy control allows for greater flexibility in optimizing etch characteristics.

Plasma Generation in ICP Systems

In an ICP system, an RF power source (typically 13.56 MHz) drives a coil surrounding a dielectric chamber, inducing an alternating magnetic field. This field accelerates electrons, ionizing the process gas (e.g., SF₆, Cl₂, or HBr) to form a high-density plasma. A separate RF bias applied to the substrate controls the ion energy, enabling precise control over etch directionality and selectivity. The high plasma density enhances etch rates, while low ion energies minimize substrate damage, making ICP etching ideal for delicate nanoscale features.

Silicon Etching Chemistry

Silicon etching in ICP systems typically involves halogen-based chemistries, with fluorine, chlorine, and bromine being the most common reactive species. Fluorine-based gases like SF₆ produce highly reactive F* radicals, leading to isotropic etching due to their high chemical reactivity. Chlorine (Cl₂) and bromine (HBr) chemistries, often combined with passivation gases like O₂ or C₄F₈, enable anisotropic etching by forming protective sidewall layers (e.g., SiOₓFᵧ or SiBrₓ) that inhibit lateral etching. The choice of chemistry depends on the desired etch profile, selectivity, and surface quality.

Process Parameters in ICP Etching

The performance of ICP etching is governed by several key parameters, including RF power, bias power, gas composition, pressure, and substrate temperature. These parameters are tuned to achieve specific etch characteristics, such as rate, anisotropy, selectivity, and uniformity.

RF Power and Bias Power

The ICP RF power controls plasma density, with higher power increasing ion and radical concentrations, thus enhancing etch rates. Typical ICP power ranges from 500 W to 2000 W. The bias power, applied to the substrate, determines ion energy and directionality. Low bias power (50–200 W) is used for delicate etching, while higher bias power improves anisotropy but may cause surface damage.

Gas Composition and Flow Rates

Gas selection and flow rates significantly influence etch outcomes. Common gases include SF₆ for isotropic etching, Cl₂/HBr for anisotropic etching, and C₄F₈/O₂ for passivation. Flow rates (10–100 sccm) are adjusted to balance reactive species and byproducts, ensuring stable plasma conditions. For example, SF₆/O₂ mixtures enhance etch rates by forming volatile SiF₄, while HBr/O₂ mixtures improve sidewall passivation.

Chamber Pressure

Chamber pressure, typically 1–100 mTorr, affects plasma density and ion mean free path. Lower pressures promote anisotropic etching by increasing ion directionality, while higher pressures enhance chemical etching but may reduce anisotropy. Optimal pressure depends on the target feature size and etch chemistry.

Substrate Temperature

Substrate temperature, controlled via a cooled chuck, influences reaction kinetics and passivation layer formation. Temperatures between 0°C and 50°C are common, with lower temperatures favoring passivation and higher temperatures enhancing chemical etching. Precise temperature control is critical for nanoscale features, where small variations can alter etch profiles.

Etch Mechanisms in Silicon ICP Etching

ICP etching of silicon involves a combination of physical and chemical mechanisms, including ion bombardment, chemical reaction, and passivation. These mechanisms interact to determine the etch profile, rate, and surface quality.

Chemical Etching

Chemical etching occurs when reactive radicals (e.g., F*, Cl*) react with silicon to form volatile byproducts (e.g., SiF₄, SiCl₄). Fluorine-based etching is highly isotropic due to the spontaneous reaction of F* with silicon, making it suitable for rapid material removal but less ideal for high-aspect-ratio features. Chlorine and bromine chemistries, being less reactive, require ion assistance for efficient etching, enabling better control over anisotropy.

Physical Etching

Physical etching involves ion bombardment, where energetic ions (e.g., Ar⁺, Cl⁺) sputter silicon atoms from the surface. While this enhances etch directionality, excessive ion energy can cause lattice damage or microtrenching. In ICP systems, low ion energies (10–100 eV) are preferred to minimize damage while maintaining anisotropy.

Passivation and the Bosch Process

Passivation is critical for anisotropic etching, particularly in deep reactive ion etching (DRIE). The Bosch process, a widely used ICP etching technique, alternates etching (SF₆) and passivation (C₄F₈) cycles to create high-aspect-ratio structures. During the etch cycle, SF₆ removes silicon isotropically, while the passivation cycle deposits a fluorocarbon polymer on sidewalls, protecting them from lateral etching. This cyclic process produces scalloped sidewalls but achieves aspect ratios exceeding 50:1.

Applications in Micro and Nanoscale Devices

ICP etching is indispensable in the fabrication of silicon-based micro and nanoscale devices, including integrated circuits (ICs), MEMS, and nanophotonic devices. Its ability to create precise, high-aspect-ratio features makes it a preferred technique in semiconductor manufacturing.

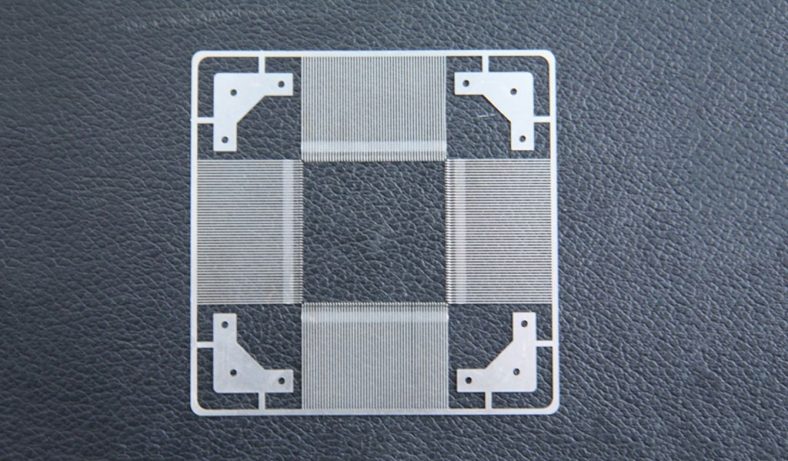

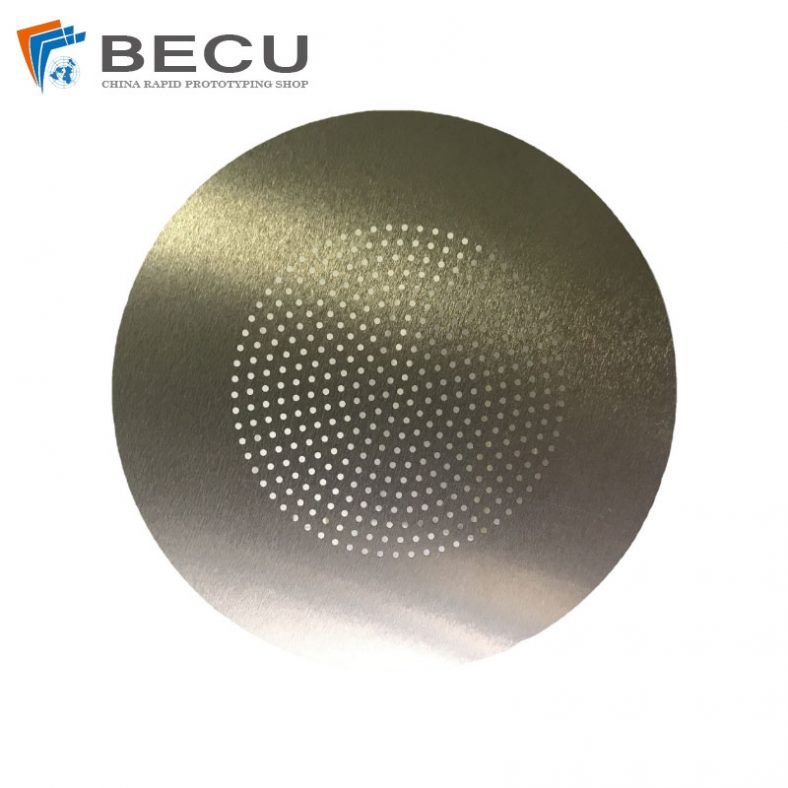

Integrated Circuits

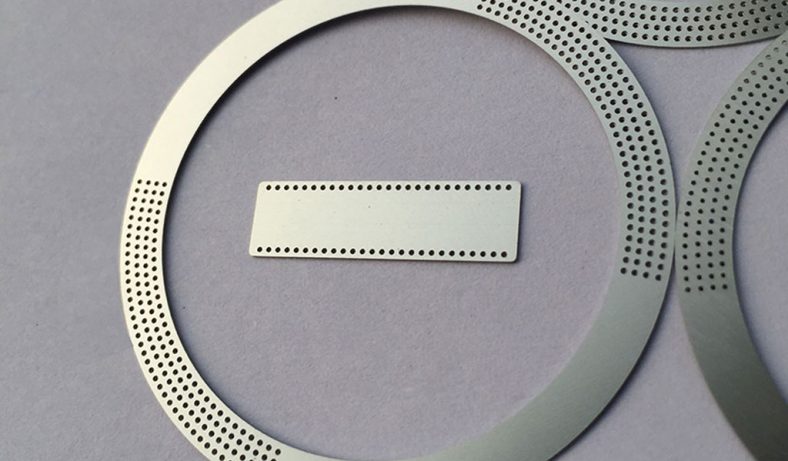

In IC fabrication, ICP etching is used to pattern polysilicon gates, shallow trench isolation (STI) structures, and through-silicon vias (TSVs). High selectivity to underlying layers (e.g., SiO₂, Si₃N₄) and smooth sidewalls are critical for ensuring device performance. For example, HBr/Cl₂-based etching is employed for gate patterning, achieving sub-10 nm feature sizes in advanced nodes.

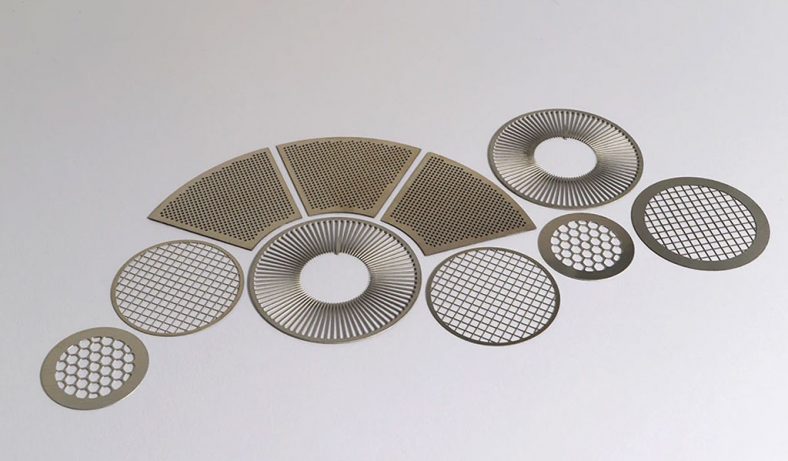

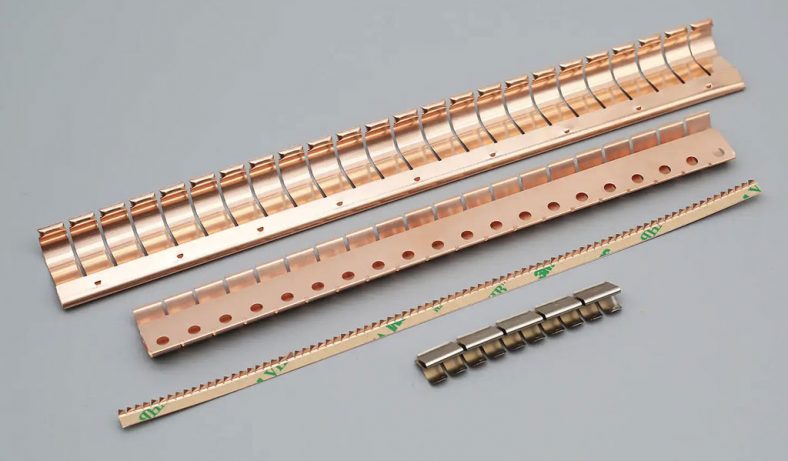

Microelectromechanical Systems (MEMS)

MEMS devices, such as accelerometers, gyroscopes, and microfluidic channels, rely on ICP etching to create complex 3D structures. The Bosch process is particularly effective for etching deep trenches and cavities with vertical sidewalls. For instance, silicon-on-insulator (SOI) wafers are etched to form suspended microstructures, with aspect ratios tailored to specific mechanical properties.

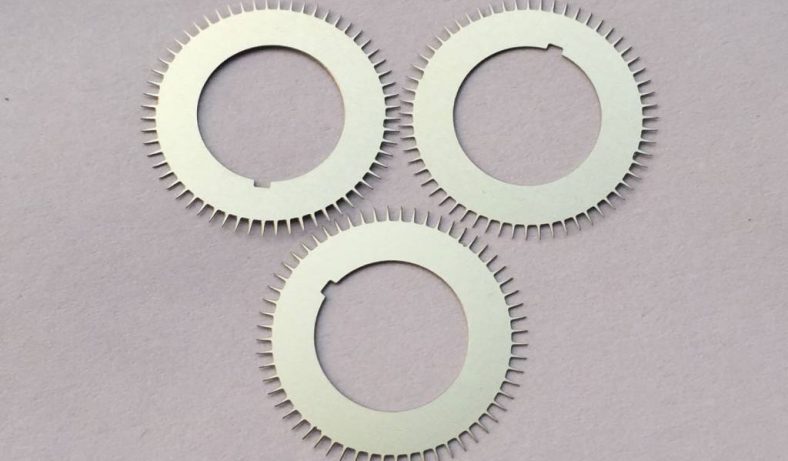

Nanophotonic and Nanoelectronic Devices

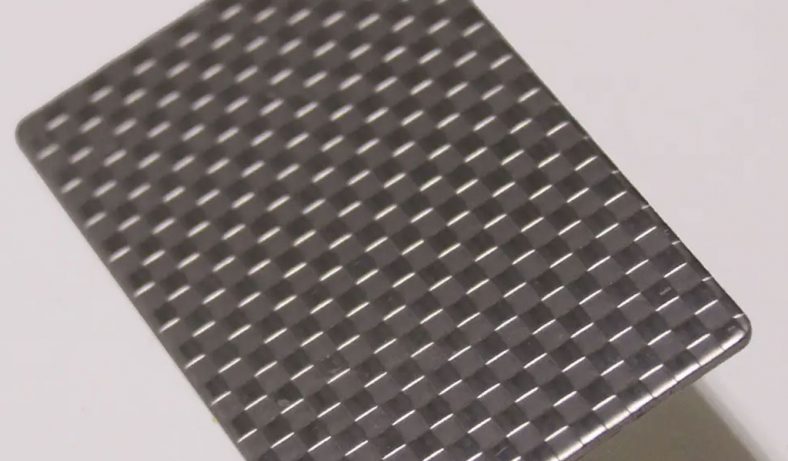

In nanophotonics, ICP etching fabricates waveguides, photonic crystals, and plasmonic structures with nanoscale precision. For example, silicon photonic waveguides require smooth sidewalls to minimize optical scattering losses. In nanoelectronics, ICP etching patterns nanowire transistors and quantum dots, where sub-5 nm feature control is essential.

Comparison of ICP Etching Chemistries

The choice of etching chemistry significantly impacts etch performance. Below is a detailed comparison of common ICP etching chemistries for silicon.

| Chemistry | Primary Gas | Passivation Gas | Etch Rate (µm/min) | Anisotropy | Selectivity to SiO₂ | Applications |

|---|---|---|---|---|---|---|

| Fluorine-based | SF₆ | O₂, C₄F₈ | 5–20 | Low–Moderate | 10:1–50:1 | Bosch process, isotropic etching |

| Chlorine-based | Cl₂ | O₂, HBr | 1–5 | High | 50:1–100:1 | Gate patterning, STI |

| Bromine-based | HBr | O₂, C₄F₈ | 0.5–3 | Very High | 100:1–200:1 | High-aspect-ratio TSVs |

| Mixed | SF₆/Cl₂/HBr | O₂, C₄F₈ | 2–10 | Moderate–High | 20:1–100:1 | MEMS, nanophotonics |

Notes: Etch rates depend on RF power, pressure, and gas flow. Selectivity is relative to thermal SiO₂. Anisotropy is qualitative, based on sidewall verticality.

Advancements in ICP Etching Technology

Recent advancements in ICP etching have focused on improving precision, uniformity, and compatibility with emerging materials and device architectures. These developments address challenges in scaling to sub-5 nm nodes and integrating novel materials like 2D materials and III-V semiconductors.

Atomic Layer Etching (ALE)

Atomic layer etching (ALE) is an emerging technique that enhances ICP etching precision by removing material one atomic layer at a time. ALE alternates self-limiting chemical adsorption (e.g., Cl₂ on silicon) with low-energy ion bombardment to desorb reaction products. This cyclic process achieves sub-nanometer control, making it ideal for FinFETs and gate-all-around (GAA) transistors.

Cryogenic ICP Etching

Cryogenic ICP etching, performed at temperatures below -100°C, enhances anisotropy by reducing chemical etching and promoting physical etching. SF₆/O₂-based cryogenic etching produces ultra-smooth sidewalls and high aspect ratios, suitable for silicon nanowire and photonic applications. However, cryogenic systems require specialized hardware, increasing process complexity.

Machine Learning in Process Optimization

Machine learning (ML) is increasingly applied to optimize ICP etching parameters. ML models predict etch profiles, rates, and uniformity based on input parameters, reducing trial-and-error in process development. For example, neural networks trained on etch data can recommend optimal RF power and gas ratios for specific feature sizes, improving throughput and yield.

Challenges and Limitations

Despite its advantages, ICP etching faces challenges that limit its performance in certain applications. These include sidewall roughness, microloading effects, and plasma-induced damage.

Sidewall Roughness

Sidewall roughness, particularly in the Bosch process, arises from cyclic scalloping and can degrade device performance (e.g., optical losses in waveguides). Smoothing techniques, such as post-etch annealing or wet cleaning, are often required, adding process steps.

Microloading Effects

Microloading, where etch rates vary with feature density, is a common issue in ICP etching. Dense patterns etch slower due to reactant depletion, while isolated features may over-etch. Advanced gas pulsing and chamber design mitigate microloading, but complete elimination remains challenging.

Plasma-Induced Damage

High-energy ions and UV radiation in ICP plasmas can cause lattice damage or charge buildup in silicon, affecting device reliability. Low-bias etching and post-etch treatments (e.g., thermal annealing) reduce damage but may not fully eliminate defects in ultra-thin layers.

Future Directions

The future of ICP etching lies in addressing the demands of next-generation devices, including 3D integrated circuits, quantum computing, and flexible electronics. Key research areas include:

- Hybrid Etching Techniques: Combining ICP with ALE or wet etching to achieve atomic-scale precision and damage-free surfaces.

- Sustainable Chemistries: Developing environmentally friendly etch gases (e.g., non-fluorinated alternatives) to reduce greenhouse gas emissions.

- Integration with Novel Materials: Adapting ICP etching for 2D materials (e.g., graphene, MoS₂) and heterogeneous integration in chiplet-based architectures.

Conclusion

ICP etching of silicon is a pivotal technology in the fabrication of micro and nanoscale devices, offering unparalleled control over feature size, anisotropy, and selectivity. Its versatility, enabled by tunable process parameters and advanced chemistries, has made it indispensable in semiconductor manufacturing, MEMS, and nanophotonics. Ongoing advancements, such as ALE, cryogenic etching, and ML-driven optimization, promise to extend its capabilities to meet the challenges of sub-5 nm nodes and emerging device paradigms. Despite challenges like sidewall roughness and plasma-induced damage, ICP etching remains a cornerstone of modern microfabrication, driving innovation in electronics and beyond.